# SM8521 CONTENTS

| DESCRIPTION2                                                       |

|--------------------------------------------------------------------|

| FEATURES 2                                                         |

| PIN CONNECTIONS 3                                                  |

| BLOCK DIAGRAM4                                                     |

| PIN DESCRIPTION5                                                   |

| ABSOLUTE MAXIMUM RATINGS 6                                         |

| RECOMMENDED OPERATING CONDITIONS 6                                 |

| DC CHARACTERISTICS7                                                |

| SM85CPU8                                                           |

| Register Lineup                                                    |

| Address Space                                                      |

| ROM Area                                                           |

| Register File Area                                                 |

| RAM Area                                                           |

| Data Format                                                        |

| Bus Timing                                                         |

| SYSTEM CONTROL18                                                   |

| Oscillator Circuit                                                 |

| Clock System                                                       |

| Memory Map                                                         |

| Hardware Reset                                                     |

| Interrupt Function                                                 |

| Standby Function                                                   |

| I/O PORTS29                                                        |

| TIMER/COUNTERS 30                                                  |

| Clock Timer                                                        |

| Watchdog Timer Register (WDT)                                      |

| LCDC/DMA 33                                                        |

| VRAM Configuration                                                 |

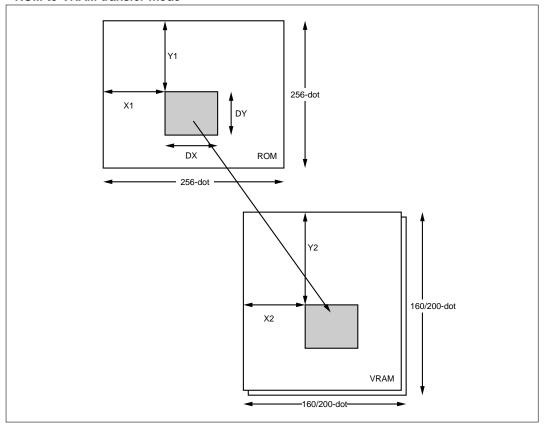

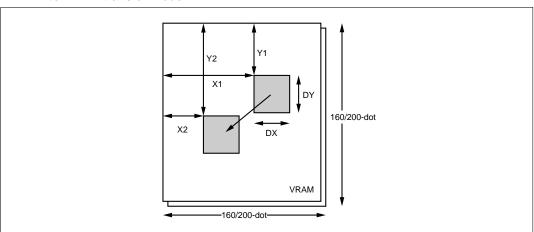

| DMA Transfer                                                       |

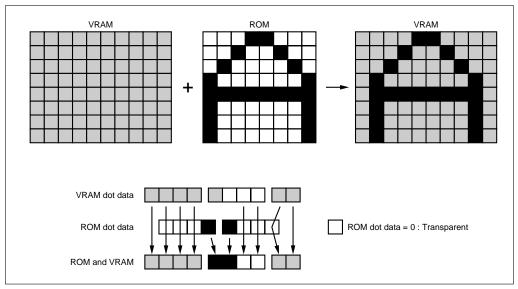

| Compound and Overwrite Mode                                        |

| Registers                                                          |

| SOUND GENERATOR 41                                                 |

| Sound Waveform Register                                            |

| Registers                                                          |

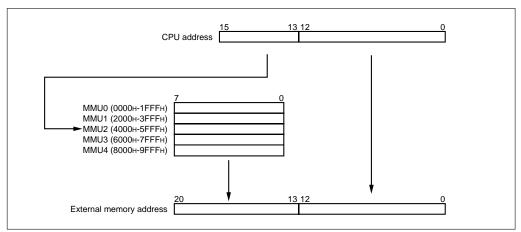

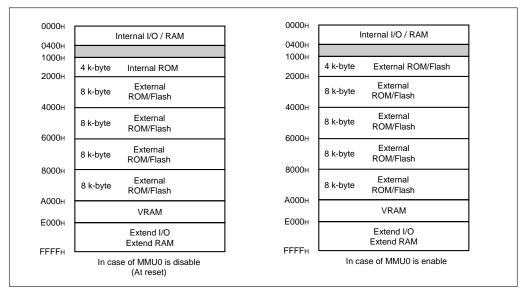

| MMU45                                                              |

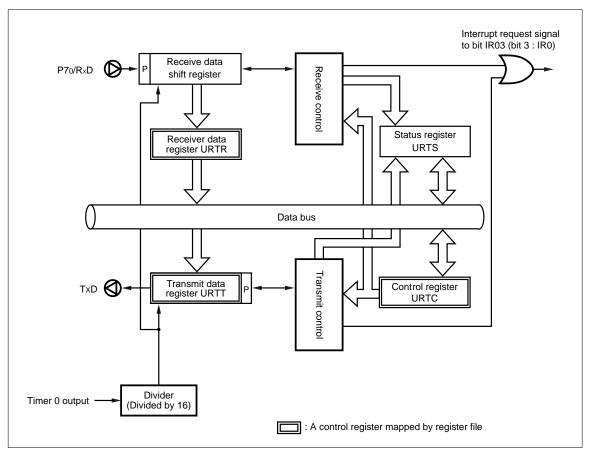

| UNIVERSAL ASYNCHRONOUS RECEIVER AND TRANSMITTER (UART) INTERFACE47 |

| UART Transmit Data Register (URTT)                                 |

| UART Receive Data Register (URTR)                                  |

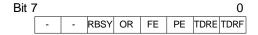

| UART Status Register (URTS)                                        |

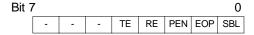

| UART Control Register (URTC)                                       |

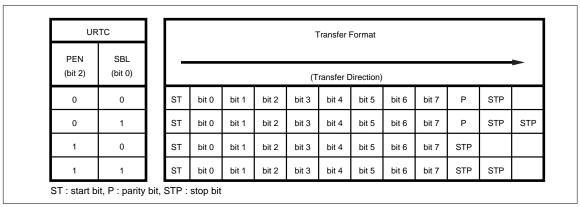

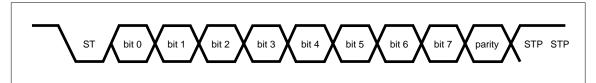

| Transfer Format                                                    |

| INSTRUCTION SET 5              | 51 |

|--------------------------------|----|

| Definition of Symbols          |    |

| Instruction Summary            |    |

| Addressing Mode                |    |

| SYSTEM CONFIGURATION EXAMPLE 5 | 55 |

# **SM8521**

## **DESCRIPTION**

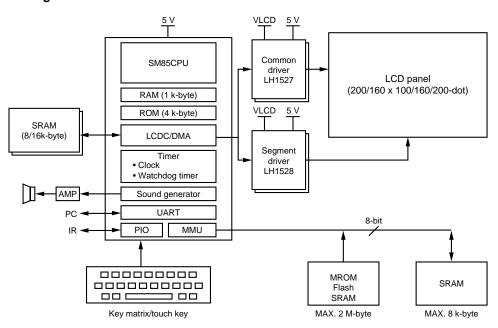

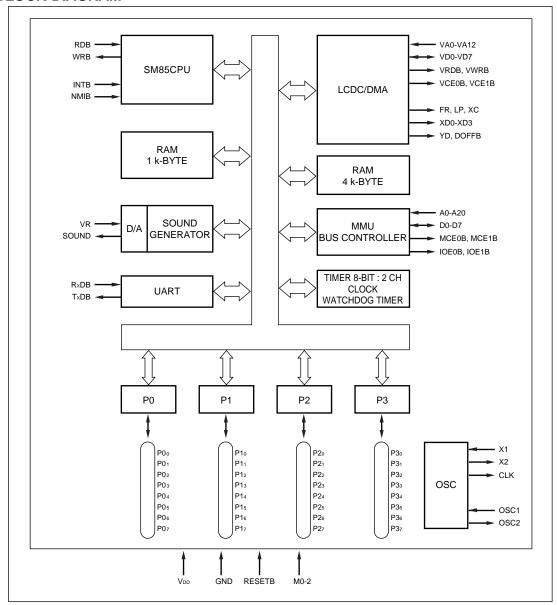

The SM8521 is a CMOS 8-bit single-chip microcomputer containing SM85CPU core and the required peripheral functions for dot matrix LCD display system. SM85CPU is an 8-bit High performance CPU with various addressing modes and High-efficiency instruction sets. SM85CPU is featured by allocating general registers on RAM to reduce overhead when calling subroutines.

The peripheral functions and memory of SM8521 contain ROM, RAM, MMU, LCD controller, DMA, sound generator, timer, serial interface (UART) and PIO.

#### **FEATURES**

• ROM capacity: 4 096 x 8 bits RAM capacity: 1 024 x 8 bits

External memory expansion

· A RAM area is used as subroutine stack

· CPU core :

- 8 bits x 8 ports (or 16 bits x 4 ports) and 16 bits x 4 ports general purpose register are used as accumulator, register pointer, and register index.

- Instruction sets (multiplication/division/bit manipulation instruction)

- Addressing mode 23 types

- System clock cycle 0.2 µs (MIN.) at 10 MHz main clock cycle

- · System clock is variable by software (system clock can be optioned to 1/2, 1/4, 1/8, 1/16, 1/32 of main-clock and 1/2 of sub-clock.)

- Built-in main clock oscillator for system clock

- · Built-in sub clock oscillator for real time clock

- Interrupts :

Non-maskable interrupts x 2 Maskable interrupts x 8

Standby modes: Halt mode/Stop mode

# 8-Bit Single-Chip Microcomputer (Controller For Hand-Held Equipment)

• I/O ports : Input/output

• Timer :

8 bits x 2 (with 8 bits prescaller) Clock timer x 1 (1 s or 1 min) Watchdog timer

• MMU :

In each 8 k-byte unit, external memory can be expanded up to MAX. 2 M bytes.

• LCD controller :

Display size 160 x 100 dots

> 160 x 160 dots 160 x 200 dots 200 x 100 dots 200 x 160 dots

black & white 4 gradations

(interframe elimination)

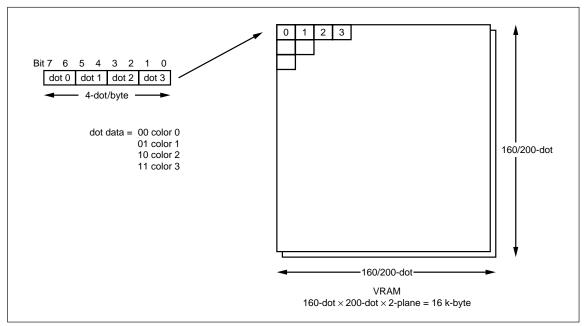

**VRAM** 160 x 200 dot x 2 phases or

200 x 160 dot x 2 phases

(required externally)

• DMA :

Transmission mode: ROM to VRAM,

VRAM to VRAM,

Extend RAM to VRAM,

VRAM to Extend RAM

Transmission data: Rectangle (Arbitrary size)

· Sound generator :

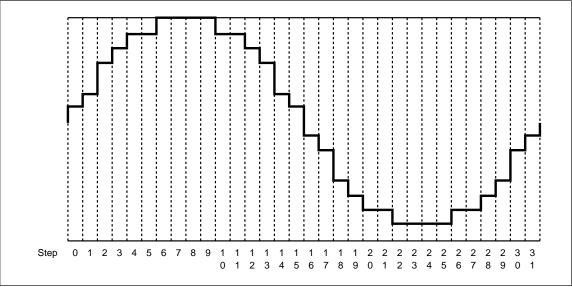

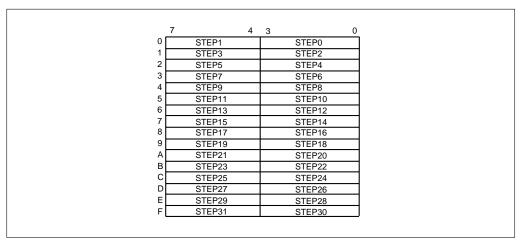

Arbitrary waveform x 2 (16-level tone, 32step/1-period waveform output)

Noise x 1 channel

• PIO :

I/O 8-bit x 4

(In each 2 bits, I/O, pull-up and open-drain can be set.)

IR carrier generator built-in.

• UART:

1 channel

Baud rate: Timer 0 output only (Timer 0 output/32)

Serial interface :

UART

8-bit clock asynchronous x 1

• Supply voltage : 4.5 to 5.5 V

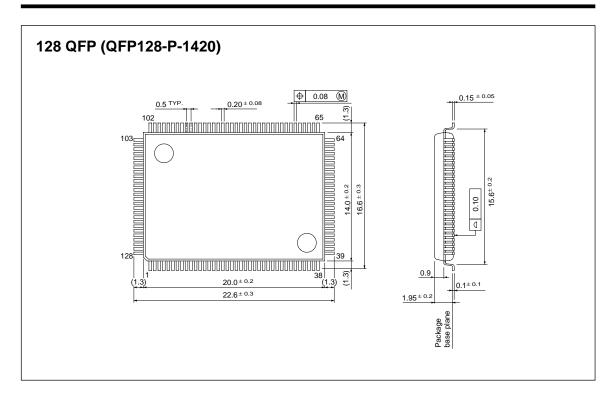

• Packages: 128-pin QFP (QFP128-P-1420)

Clock output

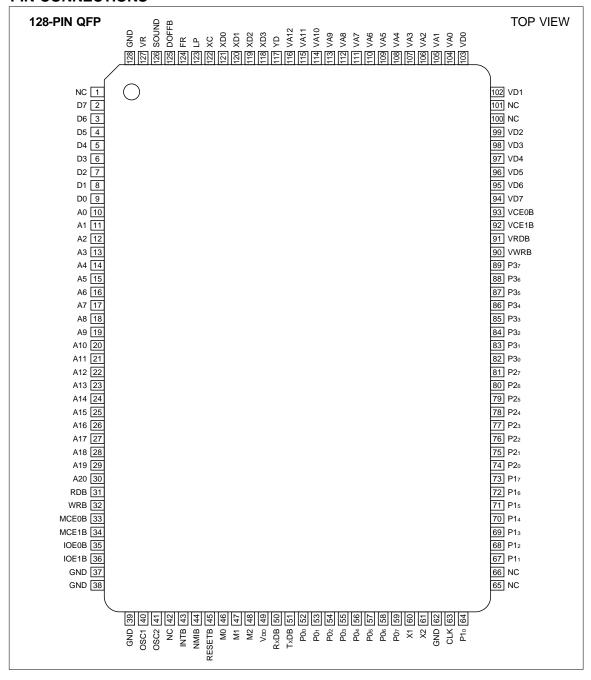

## PIN CONNECTIONS

# **BLOCK DIAGRAM**

# **PIN DESCRIPTION**

| PIN NAME                         | I/O | FUNCTION                              |  |

|----------------------------------|-----|---------------------------------------|--|

| D0-D7                            | I/O | External data bus                     |  |

| A0-A20                           | 0   | External address bus                  |  |

| MCE0B                            | 0   | Chip enable 0 (Mask ROM/flash memory) |  |

| MCE1B                            | 0   | Chip enable 1 (SRAM)                  |  |

| IOE0B                            | 0   | I/O enable 0 (address : FF00-FFFF)    |  |

| IOE1B                            | 0   | I/O enable 1 (address : FF00-FFFF)    |  |

| RDB                              | 0   | Read strobe                           |  |

| WRB                              | 0   | Write strobe                          |  |

| NMIB                             | 1   | Non-maskable interrupt                |  |

| INTB                             | 1   | External interrupt                    |  |

| VD0-7                            | I/O | VRAM data bus                         |  |

| VA0-12                           | 0   | VRAM address bus                      |  |

| VCE0B                            | 0   | VRAM chip enable 0 (A000-BFFF)        |  |

| VCE1B                            | 0   | VRAM chip enable 1(C000-DFFF)         |  |

| VRDB                             | 0   | VRAM read strobe                      |  |

| VWRB                             | 0   | VRAM write strobe                     |  |

| P0 <sub>0</sub> -P0 <sub>7</sub> | I/O | I/O port 0                            |  |

| P10-P17                          | I/O | I/O port 1                            |  |

| P2 <sub>0</sub> -P2 <sub>7</sub> | I/O | I/O port 2                            |  |

| P3 <sub>0</sub> -P3 <sub>7</sub> | I/O | I/O port 3                            |  |

| RxDB                             | I   | UART data input port                  |  |

| TxDB                             | 0   | UART data output port                 |  |

| SOUND                            | 0   | Sound output                          |  |

| VR                               | I   | D/A converter reference voltage       |  |

| FR                               | 0   | LCD drive waveform                    |  |

| LP                               | 0   | Display data latch pulse              |  |

| XC                               | 0   | Display data clock                    |  |

| XD0-XD3                          | 0   | Diaplay data                          |  |

| YD                               | 0   | Vertical timing                       |  |

| DOFFB                            | 0   | Display off                           |  |

| X1                               | I   | Main clock input                      |  |

| X2                               | 0   | Main clock output                     |  |

| CLK                              | 0   | System clock output                   |  |

| OSC1                             | I   | Subclock input                        |  |

| OSC2                             | 0   | Subclock output                       |  |

| RESETB                           | I   | Reset                                 |  |

| M0-M2                            | I   | Operation Mode (usually GND)          |  |

| Vcc, GND                         | I   | Power supply                          |  |

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER             | SYMBOL          | CONDITION                 | RATING                        | UNIT |

|-----------------------|-----------------|---------------------------|-------------------------------|------|

| Supply voltage        | V <sub>DD</sub> |                           | -0.3 to 6.5                   | V    |

| Input voltage         | Vı              |                           | -0.3 to V <sub>DD</sub> + 0.5 | V    |

| Output voltage        | Vo              |                           | -0.3 to V <sub>DD</sub> + 0.5 | V    |

| Output current        | Іон             | High-level output current | 4                             | mA   |

| Output current        | loL             | Low-level output current  | 4                             | mA   |

| Operating temperature | Topr            |                           | -10 to +60                    | °C   |

| Store temperature     | Тѕтс            |                           | -40 to +140                   | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                    | SYMBOL          | CONDITION                      | RATING          | UNIT |

|------------------------------|-----------------|--------------------------------|-----------------|------|

| Supply voltage               | V <sub>DD</sub> |                                | 4.5 to 5.5      | V    |

| System clock frequency       | <b>f</b> sys    | V <sub>DD</sub> = 4.5 to 5.5 V | 16.384 k to 5 M | Hz   |

| Maximum main clock frequency | fск             | V <sub>DD</sub> = 4.5 to 5.5 V | 10              | MHz  |

| Subclock frequency           | fsuв            | V <sub>DD</sub> = 2.7 to 5.5 V | 32.768          | kHz  |

| Operating temperature        | Topr            |                                | -10 to +60      | °C   |

## NOTE:

Be sure to RESETB when power on because internal signal reguires initialization. Normal operation is not guaranteed without hardware reset.

# **DC CHARACTERISTICS**

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, T_{OPR} = -10 \text{ to } +60^{\circ}\text{C})$

| PARA             | METER              | SYMBOL            | CONDITION                                    | MIN.                  | TYP.       | MAX.                  | UNIT | NOTE            |   |   |

|------------------|--------------------|-------------------|----------------------------------------------|-----------------------|------------|-----------------------|------|-----------------|---|---|

|                  | V <sub>IH1</sub>   |                   |                                              | V <sub>IH1</sub>      |            | 0.8 x V <sub>DD</sub> |      | V <sub>DD</sub> | V | 1 |

| Input,           | voltago            | V <sub>IL1</sub>  |                                              | 0                     |            | 0.2 x V <sub>DD</sub> | V    | V   1           |   |   |

| Input            | /oltage            | V <sub>IH2</sub>  |                                              | V <sub>DD</sub> - 0.5 |            |                       | V    | 2               |   |   |

|                  |                    | V <sub>IL2</sub>  |                                              |                       |            | 0.5                   | V    |                 |   |   |

|                  |                    | l <sub>IH1</sub>  | VIN = VDD, VDD = 5 V                         |                       |            | 10                    |      | 3               |   |   |

| Input o          | current            | I <sub>IL1</sub>  | V <sub>IH</sub> = 0 V, V <sub>DD</sub> = 5 V |                       |            | -10                   | μA   | , s             |   |   |

|                  |                    | I <sub>IL2</sub>  | V <sub>IN</sub> = 0 V, V <sub>DD</sub> = 5 V | -40                   | <b>-75</b> | -150                  | μA   | 4               |   |   |

| Output           | VoH1               |                   | lон1 = −1 mA, V <sub>DD</sub> = 5 V          | V <sub>DD</sub> - 0.5 |            |                       | V 5  | 5               |   |   |

| Output voltage V |                    | V <sub>OL1</sub>  | IoL1 = 10 mA, VDD = 5 V                      |                       |            | 0.5                   | V    | 5               |   |   |

| Resolution       |                    | on                | VR = V <sub>DD</sub> = 5 V                   |                       | 8          |                       | bits |                 |   |   |

| D/A              | Output r           | esistance         | VR = V <sub>DD</sub> = 5 V                   |                       |            | 10                    | kΩ   | 6               |   |   |

|                  | Combined tolerance |                   | VR = V <sub>DD</sub> = 5 V                   |                       | ± 0.05     | ± 0.10                | V    |                 |   |   |

|                  | IDD                |                   | fsys = 5 MHz                                 |                       | 30         | 45                    | mΛ   | 7               |   |   |

| Supply current   |                    | Іррн              | fsys = 5 MHz, HALT mode                      |                       | 15         | 18                    | mA   | 8               |   |   |

| Juppiy           | Current            | I <sub>DDS1</sub> | fsub oscillation, STOP mode                  |                       | 30         | 70                    | μA   | 9               |   |   |

|                  |                    | I <sub>DDS2</sub> | fsuв stop, STOP mode                         |                       | 1          | 6                     | μA   | 10              |   |   |

#### NOTES:

- Applicable pins: P0o-P07, P1o-P17, P2o-P27, P3o-P37, D0-D7, VD0-VD7, X1, M0-M2

- 2. Applicable pins: RESETB, OSC1, RxDB, NMIB, INTB

pull-up resistor)

- 4. Applicable pins: RESETB, P0<sub>0</sub>-P0<sub>7</sub>, P1<sub>0</sub>-P1<sub>7</sub>, P2<sub>0</sub>-P2<sub>7</sub>, P3<sub>0</sub>-P3<sub>7</sub> (connected pull-resistor)

D7, A0-A20, MCE0B, MCE1B, IOE0B, IOE1B, RDB, WRB, VA0-VA12, VCE0B, VCE1B, VWRB, TxDB, XC, LP, FR,

CLK, XD0-XD3

6. No load condition,  $V_{DD} = 5 \text{ V}$ , main clock = 10 MHz

- 7. No load condition,  $V_{DD} = 5$  V, sub clock in active (32.768 kHz), VR = GND, input signal fixation.

- No load condition, V<sub>DD</sub> = 5 V, sub clock in active (32.768 kHz), VR = GND, input signal fixation.

Including LCD, DMA, sound generator and any part concerned with timer operation.

- No load condition, V<sub>DD</sub> = 5 V, sub clock in active (32.768 kHz), VR = GND, input signal fixation.

- No load condition, V<sub>DD</sub> = 5 V, OSC1 = GND, VR = GND, input signal fixation.

#### SM85CPU

The SM85CPU is an 8-bit CPU with an unique architecture, developed by SHARP, and the following features.

## General purpose register architectures

There are eight 8-bit general purpose registers (also serve as four 16-bit general purpose registers) and four 16-bit general purpose registers serve as accumulator, index register, or the pointer registers.

#### General purpose register allocated at RAM

The general purpose registers access the RAM location by the register pointer RP. So pushing the register during an interrupt and passing parameter to subroutine can be executed in High speed.

#### Refined instruction set

- The instruction set contains total 67 members: 8 load instructions, 19 arithmetic instructions, 7 logic instructions, 9 program control (branch) instruction, 8 bit manipulation instructions, 8 rotate & shift instructions and 9 CPU control instructions.

- There are powerful bit manipulation instructions includes plural bits transfer, logical operation between bits, and the bit test and jump instructions that incorporates a test and condition branch in the same instruction. (Refer to Table 1)

- There are data transfer, arithmetic and conditional branch instructions for 16-bit. It can rapidly process the word-sized and long jump.

- There are 8-bit x 8-bit→16-bit multiplication and 16-bit x 16-bit→16-bit remaining 8-bit division instructions. (Unsigned arithmetic)

#### 23 address modes

The rich address modes provides optimal access to ROM, RAM and the register files.

#### Illegal instruction detecting function

When an error code is detected, a non-maskable interrupt (NMI) will be generated.

### Standby function

There are two standby modes, HALT and STOP mode, and the mode can be changed by HALT instruction or STOP instruction respectively.

Table 1 Instruction summary

| TYPE                         | INSTRUCTION                                          | NUMBER |

|------------------------------|------------------------------------------------------|--------|

| Load instruction             | CLR, MOV, MOVM, MOVW, POP, POPW, PUSH, PUSHW         | 8      |

| Arithmetic instruction       | ADC, ADCW, ADD, ADDW, CMP, CMPW, DA, DEC, DECW, DIV, | 19     |

| Antimetic instruction        | EXTS, INC, INCW, MULT, NEG, SBC, SBCW, SUB, SUBW     | 19     |

| Logic instruction            | AND, ANDW, COM, OR, ORW, XOR, XORW                   | 7      |

| Program control instruction  | BBC, BBS, BR, CALL, CALS, DBNZ, IRET, JMP, RET       | 9      |

| Bit manipulation instruction | BAND, BCLR, BCMP, BMOV, BOR, BTST, BSET, BXOR        | 8      |

| Rotate & shift instruction   | RL, RLC, RR, RRC, SLL, SRA, SRL, SWAP                | 8      |

| CPU control instruction      | COMC, CLRC, DI, EI, HALT, NOP, SETC, STOP            | 8      |

Total 67

Table 2 Addressing Mode Summary

| NAME                   | SYMBOL   | Range                                      | Operand *1                                                                           |  |  |

|------------------------|----------|--------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| Implied                |          |                                            | To specify the carry(C) and interrupt enable                                         |  |  |

| Implied                |          |                                            | (I) in the instruction code.                                                         |  |  |

| Register               | r        | r = R0-R7                                  | General register [byte]                                                              |  |  |

| Register pair          | rr       | r = RR0, RR2,, RR14                        | General register [word]                                                              |  |  |

| Register file          | R        | R = 0 to 255 (R0-R15)                      | Register file (0000H-007FH) and (0080H-00FFH)                                        |  |  |

| Tregister file         |          | N = 0 to 255 (NO-N 15)                     | [byte]                                                                               |  |  |

| Register file pair     | RR       | R = 0, 2, 254                              | Register file (0000 <sub>H</sub> -007F <sub>H</sub> ) and (0080H-00FF <sub>H</sub> ) |  |  |

| rtegister file pail    | IXIX     | (RR0, RR2,, RR14)                          | [byte]                                                                               |  |  |

| Register indirect      | @r       | r = R0-R7                                  | Memory (0000н-00FFн) [byte]                                                          |  |  |

| Register indirect      | (r)+     | r = R0-R7                                  | Memory (0000н-00FFн) [byte]                                                          |  |  |

| auto increment         | (1)+     | 1 = 100-107                                | Wellioty (0000H-001 Fil) [byte]                                                      |  |  |

| Register indirect      | —(r)     | r = R0-R7                                  | Memory (0000н-00FFн) [byte]                                                          |  |  |

| auto decrement         |          | 1 = 100-107                                | Wellioly (0000H-001 Fil) [byte]                                                      |  |  |

| Register index         | n(r)*2   | n = 00н-FFн, r = R1-R7                     | Memory (0000н-00FFн) [byte]                                                          |  |  |

| Register pair indirect | @rr      | rr = RR0, RR2, , RR14                      | Memory (0000н-FFFFн) [word/byte]                                                     |  |  |

| Register pair indirect | (rr)+    | rr = RR0, RR2, , RR14                      | Memory (0000н-FFFFн) [word/byte]                                                     |  |  |

| auto increment         | (11)1    | 11 - 1010, 1012,, 10114                    | Wellery (Goodin't i i ii) [Weller Byte]                                              |  |  |

| Register pair indirect | –(rr)    | rr = RR0, RR2, , RR14                      | Memory (0000н-FFFFн) [word/byte]                                                     |  |  |

| auto decrement         | (,       | , rate,, rater                             | [Wordsyte]                                                                           |  |  |

| Register pair index    | nn(rr)*3 | nn = 0000н-FFFFн                           | Memory (0000н-FFFFн) [word/byte]                                                     |  |  |

| rtogistor pair iridox  | (,       | rr = RR2, RR4,, RR14                       | [Word/Byte]                                                                          |  |  |

| Index indirect         | @nn(r)*2 | nn = 0000н-FFFFн                           | Memory (0000н-FFFFн) [word]                                                          |  |  |

|                        |          | r = R1-R7                                  | e.i.e.iy (coco.i. i i i i i j [ii.e.a]                                               |  |  |

| Immediate              | IM       | IM = 00 <sub>H</sub> -FF <sub>H</sub>      | The immediate data in the instruction code [byte]                                    |  |  |

| Immediate long         | IML      | IML = 0000 <sub>H</sub> -FFFF <sub>H</sub> | The immediate data in the instruction code [word]                                    |  |  |

|                        |          |                                            | Register file (0000 <sub>H</sub> -007F <sub>H</sub> ) and memory                     |  |  |

| Bit                    | b        | b = 0 to 7                                 | (0080н-00FFн, FF00н-FFFFн) [bit] (1 bit of 1 byte                                    |  |  |

|                        |          |                                            | pointed by R, n(r) and DAp)                                                          |  |  |

| Port                   | р        |                                            | Register file (0010 <sub>H</sub> -0017 <sub>H</sub> ) [byte]                         |  |  |

| Relative               | RA       | PC - 128 to PC + 127                       | Program memory (1000н-FFFFн)                                                         |  |  |

| Direct                 | DA       | DA = 0000 <sub>H</sub> -FFFF <sub>H</sub>  | Memory (0000н-FFFFн) [byte]                                                          |  |  |

| Direct short           | DAs      | DAs = 1000 <sub>H</sub> -1FFF <sub>H</sub> | Program memory (1000н-1FFFн)                                                         |  |  |

| Direct special page    | DAp      | DAp = FF00 <sub>H</sub> -FFFF <sub>H</sub> | Program memory (FF00н-FFFFн) [byte]                                                  |  |  |

| Direct indirect        | @DA      | DA = 0000 <sub>H</sub> -FFFF <sub>H</sub>  | Memory (0000н-FFFFн)                                                                 |  |  |

<sup>\*1</sup> The data indicated by [ ] is the unit of possible to use in Load and Arithmetic Instructions.

<sup>\*2</sup> R0 can not be used.

<sup>\*3</sup> RR0 can not be used.

# **Register Lineup**

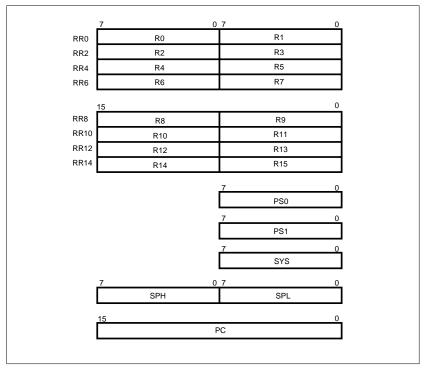

Fig. 1 shows the SM85CPU register lineup. The CPU internal register consists of eight 8-bit general purpose registers (R0-R7), four 16-bit general purpose registers

(RR8-RR14), a program counter (PC) and four other control registers. (The R0-R7 can be also used as four 16-bit general purpose registers (RR8-RR14).)

Fig. 1 Register Lineup

#### **GENERAL PURPOSE REGISTER**

The eight 8-bit general purpose registers R0-R7 and all eight 16-bit general purpose registers (RR0-RR14) are available for use as accumulator, index register and pointer registers. (The R0 and RR0 cannot be used as index register)

The other eight 8-bit registers R8-R15 cannot be used as 8-bit general purpose register and as member of the register file. (about register file, refer to "Address Space.")

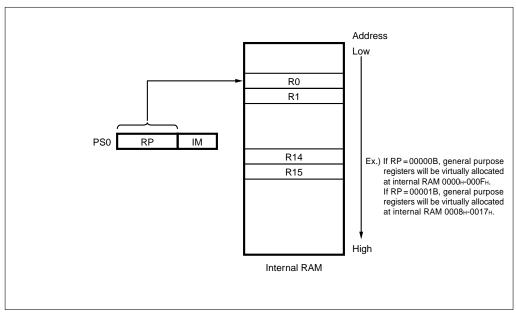

The feature of the SM85CPU architecture is that general purpose registers are virtually allocated at 16-byte internal RAM. Actually, if the CPU accesses general purpose registers, the designated RAM will be accessed by the 5-bit register pointer (RP)\*. When RP = 00000B, the registers occupy the first

16 bytes starting at 0000<sub>H</sub>. Incrementing the field, RP = 00001B, shifts the mapping by eight bytes so that the registers start at 0008<sub>H</sub>. As a result, the general purpose registers can be switched in 8-byte unit to any RAM location within 0000<sub>H</sub>-00FF<sub>H</sub>.

Although the general purpose registers are members of the register file, which stores the data onto actual RAM, is different from the other members (control registers).

That is, general purpose registers can be referred as registers, as register file (allocated at 0000H-000FH) and as RAM accessing by all addressing modes.

About register pointer (RP), refer to "Processor status 0 (PS0)".

#### **CPU CONTROL REGISTER**

The SM85CPU has the following control register: processor status PS0, processor status PS1, system configuration register SYS, stack pointer SPH, SPL and program counter PC. All control register except the program counter PC are members of the register file and accessible by the register file R and the register file pair RR addressing modes.

#### Processor status 0 (PS0)

The processor status PS0 is an 8-bit readable/writable register containing 2 fields, the upper 5-bit is register pointer (RP) and the lower 3-bit is interrupt mask.

| Bit 7 | 7   |     |     |     |     |     |     | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

|       | PR4 | PR3 | PR2 | PR1 | PR0 | IM2 | IM1 | IM0 |

Bits 7 to 3: Register pointer (RP)

This gives, in 8 bytes unit, the starting address in RAM for general purpose registers.

Bits 2 to 0 : Interrupt mask bits (IM)

| BIT | CONTENT                                           |

|-----|---------------------------------------------------|

| 000 | All maskable interrupts recognized                |

| 001 | All maskable interrupts recognized                |

| 010 | Maskable interrupts with level 1 to 12 recognized |

| 011 | Maskable interrupts with level 1 to 10 recognized |

| 100 | Maskable interrupts with level 1 to 8 recognized  |

| 101 | Maskable interrupts with level 1 to 6 recognized  |

| 111 | Maskable interrupts with level 1 tto 4 recognized |

| 111 | Maskable interrupts with level 1 to 2 recognized  |

Fig. 2 Register Pointer (RP) Setting Example

# Processor status 1 (PS1)

The processor status PS1 is an 8-bit readable/writable register and consists of eight flag bits. These flags can be used as the condition codes for the conditional branch instructions. When CPU generates an interrupt, the content of processor status PS1 and the value of program counter PC automatically are pushed onto stack.

Bit 7 0

C Z S V D H B I

Bit 7: Carry (C)

It indicates that generated a carry in operation.

Bit 6: Zero (Z)

It indicates that the operation result is zero.

Bit 5: Sign (S)

It indicates that the operation result is negative (Sign bit = '1').

Bit 4: Overflow (V)

Executes the operation with the signed value. If the operation result cannot indicate complement on two, then the bit will be '1'.

Bit 3: Decimal adjustment (D)

It indicates that the last arithmetic operation is a subtraction.

Bit 2: Half carry (H)

It indicates that generated a carry between bit 3 and 4.

Bit 1 : Bit (B)

It indicates that the result of the last bit manipulation.

Bit 0: Interrupt enable (I)

This is a flag which enables/disables all maskable interrupt.

# System configuration register (SYS)

The system configuration register SYS is an 8-bit readable/writable register which sets the external memory expansion modes and selects 8-bit/16-bit stack pointer.

Bit 7 0

- | SPC | - | - | MCNF2 | MCNF1 | MCNF0

Bit 7 : Sets '0'

Bit 6: Stack pointer configuration (SPC)

| BIT | CONTENT                |

|-----|------------------------|

| 0   | 8-bit (SPL only)       |

| 1   | 16-bit (both SPL, SPH) |

Bits 5 to 3 : Set '0'

Bits 2 to 0: Memory configuration (MCNF2-0)

| BIT               | CONTENT                                      |

|-------------------|----------------------------------------------|

| 000               | External memory expansion disable.           |

| 110               | External memory expansion mode (64 k bytes*) |

| Other combination | Do not use.                                  |

\*: In ROM space (60 k bytes), the field beyond the internal ROM is the external memory access field.

## Stack pointer (SPL, SPH)

The stack pointer SPL, SPH are 8-bit readable/ writable register and show the stack address. The bit SPC of the system configuration (SYS) specifies whether the stack pointer is 8 (SPL only) or 16 (both SPL and SPH) bits long.

## Program counter (PC)

The program counter (PC) is a pointer for program memory and contains the starting address for the next instruction.

| В | it 15 | , |  |  |  |  |  |  | 0 |

|---|-------|---|--|--|--|--|--|--|---|

|   |       |   |  |  |  |  |  |  |   |

The program counter PC is initialized to  $1020_{\text{H}}$  after hardware reset. That is, the application program starts executing from the address  $1020_{\text{H}}$  after hardware reset.

# **Address Space**

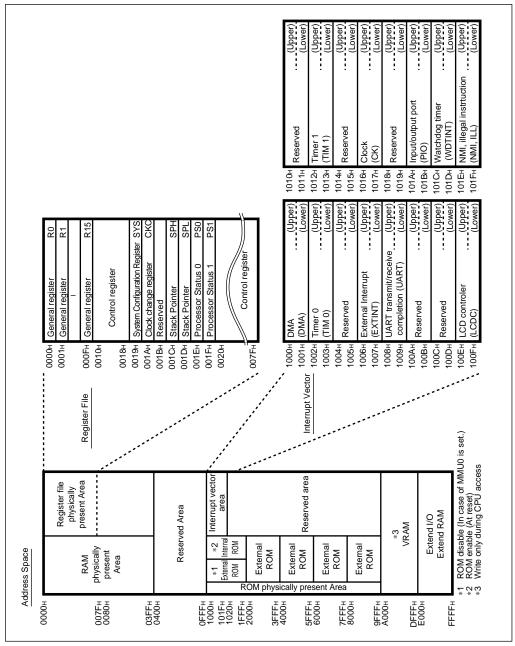

The SM85CPU has a 64 k-byte address space, which is divided into RAM (0000H-0FFFH) and ROM (1000H-FFFFH) areas. The address 0000H-007FH are both shared by RAM and register file. Fig. 9-1 shows the SM8521 Memory Map.

The RAM and register file allocated at 0000H-007FH can be selected by the addressing mode designated by instructions.

The SM8521 supports an Memory Management Unit used to external memory area expantion. Refer to "Memory Management Unit (MMU)".

#### **ROM Area**

ROM area starts at the address 1000<sub>H</sub> of the space address. The first portion (1000<sub>H</sub>-101F<sub>H</sub>) is reserved for the interrupt vector table. Each 2 bytes entry in the vector table contains the address of interrupts. When an interrupt encountered, the CPU jumps to the corresponding branch address of vector table for program executing. The address 1020<sub>H</sub> marks the start of the user program area itself. Executing always starts at 1020<sub>H</sub> after hardware reset.

# Register File Area

The register file is allocated between 0000<sub>H</sub> and 007F<sub>H</sub>. The first 16 bytes (0000<sub>H</sub>-000F<sub>H</sub>) area are general registers. The remainder is for CPU control registers, peripherals control register and data register.

#### **RAM Area**

The RAM area starts at the beginning  $0000_{\rm H}$  of the address space. It overlaps the register file for the address  $0000_{\rm H}\text{-}007F_{\rm H}$ .

This arrangement is to shorten the instruction length as much as possible and to permit the use with both RAM and the register file for faster execution.

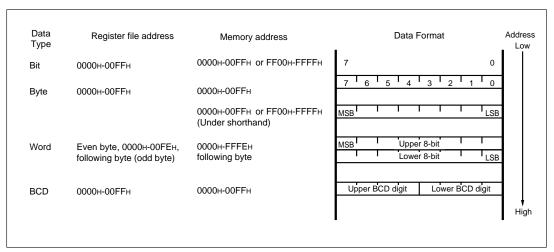

Fig. 3 Register File/Memory Data Formats

#### **Data Format**

The SM85CPU supports four data types: bit, 4-bit BCD, byte, and word data.

#### **REGISTER FILE DATA FORMATS**

The register file (0000H-007FH) and RAM (0080H-00FFH) accessible with register file R and register file pair RR addressing support processing for all 4 data types: bit, 4-bit BCD, byte, and word data. Fig. 3 shows the data layout in the register file.

#### • Bit data (register file)

Bit manipulation instructions access bit data in the register by register file R addressing, which gives the byte address in the register file (0000<sub>H</sub>-007F<sub>H</sub>), or RAM (0080<sub>H</sub>-00FF<sub>H</sub>), and the operand b, which gives the bit number within the byte.

#### Byte data (register file)

Instructions access the byte data in the register file by register file R addressing, which gives the byte data address in the register file (0000<sub>H</sub>-007F<sub>H</sub>) or RAM (0080<sub>H</sub>-00FF<sub>H</sub>).

#### • Word data (register file)

Instructions access word data in the register file by register file pair RR addressing, which gives the word address, even and 2 bytes address, in the register file (0000H-007FH) or RAM (0080H-00FFH). The address must be even (0, 2, 4,..., 254). Specifying an odd address leads to unreliable results.

#### • BCD data (register file)

The decimal adjust instruction (DA), used to adjust BCD digits after an odd or subtraction, accesses a BCD data byte in the register file by register file R addressing.

#### · Notice for the general register on register file

The general registers are the first 16 bytes (0000H-000FH) in the register file. They can be accessed as byte-sized by register file R addressing and as word-sized by register file pair RR addressing.

#### MEMORY DATA FORMATS

The memory area (ROM and RAM 0000<sub>H</sub>-FFFF<sub>H</sub>) supports processing for all 4 data types: bit, 4-bit BCD, byte and word data. However, bit data is limited to the ranges (0000<sub>H</sub>-00FF<sub>H</sub>, FF00<sub>H</sub>-FFFF<sub>H</sub>), and 4-bit BCD data to the ranges 0000<sub>H</sub>-00FF<sub>H</sub>. Fig. 3 shows the data layout in memory.

#### • Bit data (memory)

Bit manipulation instructions access bit data in memory by register index n(r) addressing, which gives the byte address in the range (0000<sub>H</sub>-00FF<sub>H</sub>), or by direct special page DAp addressing, which gives the byte address in the range (FF00<sub>H</sub>-FFFF<sub>H</sub>), and the operand b, which gives the bit number within the byte.

#### • Byte data (memory)

Instructions access the byte data in memory by shorthand (0000<sub>H</sub>-00FF<sub>H</sub> or FF00<sub>H</sub>-FFFF<sub>H</sub>) or full (0000<sub>H</sub>-FFFF<sub>H</sub>) address.

#### Word data (memory)

Instructions access the word data, continue 2 bytes, in memory by shorthand (0000 $_{\rm H}$ -00FF $_{\rm H}$  or FF00 $_{\rm H}$ -FFFF $_{\rm H}$ ) or full (0000 $_{\rm H}$ -FFFF $_{\rm H}$ ) address.

Unlike word data in the register file, the address can be even or odd.

#### BCD data (memory)

The decimal adjust instruction (DA), used to adjust BCD digits after an odd or subtraction, accesses a BCD data byte in memory by register index @r addressing.

#### Notice for general register on memory

The general registers are actually in a RAM area specified by register pointer RP, so they can be read and modify directly as RAM. While programming, the programmer must take care to arrange program data so that other RAM operations do not destroy general registers content.

# **Bus Timing**

The SM85CPU is variable for system clock. The bit FCPUS2-FCPUS0 (bits 5 to 3 : CKKC) of the clock changing register CKKC can select system clock to 1/2, 1/4, 1/8, 1/16 and 1/32 of the main clock and 1/2 of sub-clock. The CPU operates at 1/32 clock of the main clock after hardware reset.

#### INTERNAL MEMORY ACCESS TIMING

The read cycle of internal RAM is 2 cycles. The internal RAM supports 2 cycles for reading or writing.

#### **EXTERNAL MEMORY ACCESS TIMING**

The external memory supports 2 cycles for reading or writing. Fig. 5 shows the read timing and Fig. 6 shows the write timing.

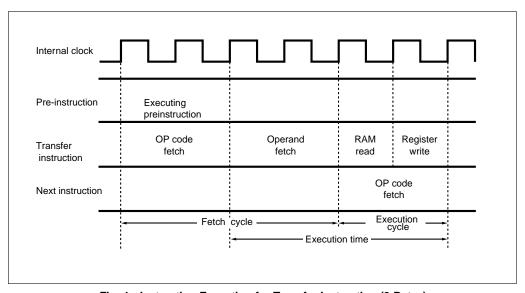

#### INSTRUCTION PREFETCH

The SM85CPU, which execution cycle overlaps with the OP code, fetches next instruction OP code during one instruction execution cycle. For example, the execution time for 2 bytes instructions (MOV R, r) of transferring the RAM contents to a register is 4 cycles.

Fig. 4 Instruction Execution for Transfer Instruction (2 Bytes)

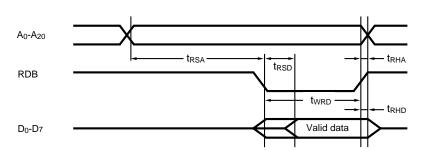

# • External memory access timing (read timing)

$t_{\mbox{\scriptsize RSA}}$ : The time between address firm and RDB signal falling Low level firm.

$t_{\mbox{\scriptsize RSD}}$  : The time between RDB signal firm and input valid data firm.

twrd: RDB signal Low level width.

$t_{\mbox{\scriptsize RHA}}$  : The time between RDB signal rising High level firm and address change.

$t_{\text{RHD}}$  : The time between RDB signal rising High level firm and output data floating.

Load capacitance is 50 pF.

Fig. 5 External Memory Access Timing (Read Timing)

## **Operating condition**

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, T_{OPR} = -10 \text{ to } 60^{\circ}\text{C})$

| PARAMETER              | SYMBOL       | MIN.      | TYP. | MAX.        | UNIT | NOTE |

|------------------------|--------------|-----------|------|-------------|------|------|

| Address setup time     | <b>t</b> rsa |           | tsys | tsys + 50   | ns   | 1    |

| Read data setup time   | <b>t</b> rsd |           |      | tsys/2 - 30 | ns   | 1    |

| RDB signal pulse width | twrd         | tsys - 50 |      | tsys        | ns   | 1    |

| Address hold time      | <b>t</b> rha | 0         |      |             | ns   |      |

| Read data hold time    | <b>t</b> RHD | 0         |      |             | ns   |      |

## NOTE:

tsvs: The system clock period (main clock x 1/2) when the low order 3 bits in the clock change register FCPUS2-FCPUS0 are 100<sub>B</sub>.

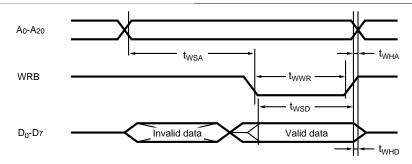

# • External memory access timing (write timing)

twsa: The time between address firm and WRB signal falling Low level firm.

twsp: The time between WRB signal rising High level firm and output valid data firm.

twwr: WRB signal Low level width.

twha: The time between WRB signal rising High level firm and address change.

$t_{\mbox{\scriptsize WHD}}$ : The time between WRB signal rising High level firm and output data floating.

Load capacitance is 50 pF.

Fig. 6 External Memory Access Timing (Write Timing)

# Operating condition

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, T_{OPR} = -10 \text{ to } 60^{\circ}\text{C})$

| PARAMETER              | SYMBOL       | MIN.      | TYP.         | MAX.      | UNIT | NOTE |

|------------------------|--------------|-----------|--------------|-----------|------|------|

| Address setup time     | twsa         |           | <b>t</b> sys | tsys + 50 | ns   | 1    |

| Data setup time        | twsp         | tsys - 50 | tsys + 30    |           | ns   | 1    |

| WRB signal pulse width | twwr         | tsys - 60 |              | tsys      | ns   | 1    |

| Address hold time      | <b>t</b> wha | 10        |              |           | ns   |      |

| Data hold time         | <b>t</b> whd | 10        |              |           | ns   |      |

#### NOTE:

tsvs: The system clock period (main clock x 1/2) when the low order 3 bits in the clock change register FCPUS2-FCPUS0 are 100<sub>B</sub>.

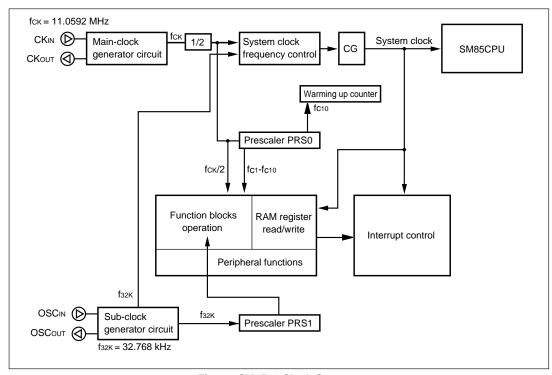

# SYSTEM CONTROL Oscillator Circuit

The SM8521 is built-in the main-clock and subclock oscillator circuits for generating clock signal. The main-clock oscillator circuit is applied to 1.5 to 10 MHz. The sub-clock oscillator circuit is applied to 32.768 kHz.

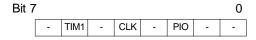

# **Clock System**

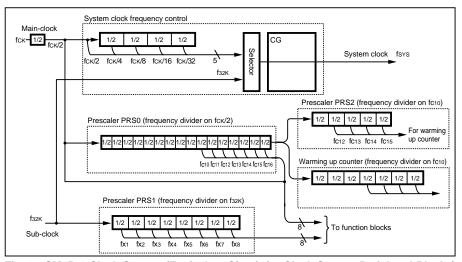

The SM8521 uses the main-clock and sub-clock oscillator circuits to generate the required clock.

The system clock, leads CPU operation, is one of the five clocks which divides the main-clock ( $f_{CK}$ ) into 1/2, 1/4, 1/8, 1/16 and 1/32. It also selects from sub-clock ( $f_{32K}$ ). In addition, the clocks supplied to the peripheral functions are  $f_{C1}$ - $f_{C1}$ 0 divided by the prescaler PRS0 and derived from the 1/2 clock of main-clock ( $f_{CK}$ /2), and  $f_{X1}$ - $f_{X8}$  divided by the prescaler PRS1 and derived from the sub-clock.

Fig. 7 SM8521 Clock System

Fig. 8 SM8521 Clock System (Equivalent Circuit for Clock System Peripheral Blocks)

# Clock change register (CKKC)

Clock change register CKKC is an 8-bit readable/ writable register containing the control of system clock change and the setting of warming up period after waking up from the STOP mode.

Clock change register CKKC is initialized to  $00\mathrm{H}$  after hardware reset.

Bit 7 : Clock change enable bit (FCPUEN)

| BIT | CONTENT                            |

|-----|------------------------------------|

| 0   | Disables system clock speed change |

| 1   | Enables system clock speed change  |

Bit 6: Main-clock stopped bit (MCKSTP)

Main-clock stopped allows switching to sub-clock used as system clock.

| BIT | CONTENT              |

|-----|----------------------|

| 0   | Main-clock operation |

| 1   | Main-clock stop      |

Bits 5 to 3 : System clock selection bits (FCPUS2-FCPUS0)

Under the bit FCPUEN = '1', if executes the STOP instruction, the bits will be valid.

| BIT      | SYSTEM CLOCK FREQUENCY             |

|----------|------------------------------------|

| 000      | System clock = (1/32) x main-clock |

| 001      | System clock = (1/16) x main-clock |

| 010      | System clock = (1/8) x main-clock  |

| 011      | System clock = (1/4) x main-clock  |

| 100      | System clock = (1/2) x main-clock  |

| 101, 110 | Reserved                           |

| 111      | System clock = (1/2) x sub-clock   |

Bit 2: Reserved bit (TFCPU)

Always write '0' to this position. Writing a '1' produces unrealiable operation.

Bits 1 to 0 : Warming up selection bits (WUPS1-WUPS10)

The bits are able to set the warming up period of after wake up from STOP mode.

|     | WARMING UP PERIOD AFTER STOP                   |

|-----|------------------------------------------------|

| BIT | MODE RELEASES                                  |

|     | (when main-clock (fcк) = 10 MHz)               |

| 00  | 218 x main-clock period (26.21 ms)             |

| 01  | 2 <sup>17</sup> x main-clock period (13.10 ms) |

| 10  | 2 <sup>16</sup> x main-clock period (6.553 ms) |

| 11  | 2 <sup>15</sup> x main-clock period (3.276 ms) |

# **Memory Map**

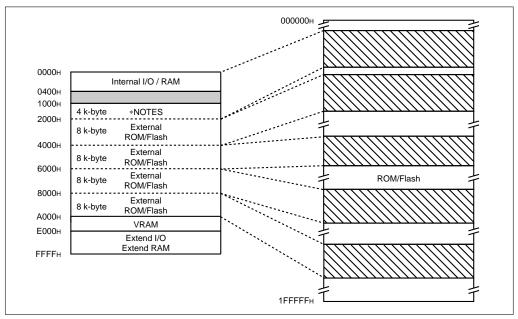

Fig.9 shows the SM8521 memory map.

Fig. 9-1 SM8521 Memory Map (1)

| Address           | Register name                 |                            | R           | R/W Initial value | Address           | Register name                     |       | &     | Initial value |

|-------------------|-------------------------------|----------------------------|-------------|-------------------|-------------------|-----------------------------------|-------|-------|---------------|

| +0000             | General purpose register R0   | 0                          | R/W         | Undefined         | 0020н             | PIO control register 0            | POC   | R/W   | н00           |

| 0001н             | General purpose register R1   |                            | R/W         | Undefined         | 0021н             | PIO control register 1            | P1C   | R/W   | н00           |

| 0002н             | General purpose register R2   |                            | R/W         | Undefined         | 0022н             | PIO control register 2            | P2C   | R/W   | н00           |

| н€000             | General purpose register R3   | 3 RRZ                      | R/W         | Undefined         | 0023н             | PIO control register 3            | P3C   | R/W   | н00           |

| 0004н             | General purpose register R4   |                            | R/W         | Undefined         | 0024н             | MMU data register 0               | MMU0  | R/W   | н00           |

| 0005H             | General purpose register R5   | 72<br>XX<br>44             | R<br>≪      | Undefined         | 0025н             | MMU data register 1               | MMU1  | R/W   | н00           |

| H9000             | General purpose register R6   |                            | R/W         | Undefined         | 0026н             | MMU data register 2               | MMU2  | R/W   | н00           |

| н2000             | General purpose register R7   | 7 KR0                      | R/W         | Undefined         | 0027н             | MMU data register 3               | MMU3  | R/W   | н00           |

| +8000             | General purpose register R8   |                            | R<br>≪      | Undefined         | 0028н             | MMU data register 4               | MMU4  | R/W   | н00           |

| <sup>+</sup> 6000 | General purpose register R9   | 9<br>2<br>2<br>2<br>2<br>3 | R<br>≪      | Undefined         | 0029н             | Reseved                           |       |       | ı             |

| 000Ан             | General purpose register R10  |                            | R.W         | Undefined         | 002Ан             | Reseved                           |       |       | ı             |

| 000Вн             | General purpose register R11  | 7<br>X<br>5                | R<br>≪      | Undefined         | 002Вн             | UART Transmit data register       | URTT  | >     | FF            |

| н 2000            | General purpose register R12  |                            | R/W         | Undefined         | 002Сн             | UART Receive data register        | URTR  | 2     | н00           |

| 000DH             | General purpose register R13  | 3 KK12                     | R.          | Undefined         | 002DH             | UART Status register              | URTS  | ď     | 0*000010      |

| 000Ен             | General purpose register R14  |                            | R.          | Undefined         | 002Ен             | UART Control register             | URTC  | R/W   | н00           |

| 000F <sup>H</sup> | General purpose register R15  | 7<br>7<br>7<br>4           | R<br>≪      | Undefined         | 002Fн             | Reseved                           |       |       | ı             |

| 0010⊬             | Interrupt enable register 0   | IE0                        | R<br>≪      | н00               | 0030н             | Control/Status register           | CCC   | R.W   | н00           |

| 0011⊬             | Interrupt enable register 1   | IE1                        | R/W         | н00               | 0031н             | Display H-timing register         | ГСН   | R/W   | 000000**      |

| 0012н             | Interrupt request register 0  | IR0                        | R/W         | н00               | 0032н             | Display V-timing register         | CCV   | R/W*1 | 0*00000       |

| 0013⊬             | Interrupt request register 1  | IR1                        | R/W         | н00               | нее00             | Reserved                          |       |       | ı             |

| 0014н             | PIO data register 0           | PO                         | R.          | н00               | 0034н             | Controler register                | DMC   | R/W   | 0*00000       |

| 0015∺             | PIO data register 1           | 7                          | R<br>M<br>M | н00               | 0035н             | Source X-coordinate register      | DMX-1 | R.W.  | н00           |

| 0016н             | PIO data register 2           | P2                         | R.W         | н00               | 9800              | Source Y-coordinate register      | DMY-1 | RW    | н00           |

| 0017н             | PIO data register 3           | P3                         | R/W         | н00               | 0037н             | X-width register                  | DMDX  | R/W   | н00           |

| 0018∺             | Reserved                      |                            | ,           | 1                 | 0038н             | Y-width register                  | DMDY  | R.W   | н00           |

| 0019⊬             | System configuration register | r SYS                      | R/W         | 0000000*          | н6600             | Destination X-coordinate register | DMX2  | RW    | н00           |

| 001Ан             | Clock change register         | CKC                        | R.          | н00               | 003Ан             | Destination Y-coordinate register | DMY2  | RW    | н00           |

| 001Вн             | Reserved                      |                            | ,           | ı                 | 003Вн             | Pallet register                   | DMPL  | R/W   | н00           |

| 001C∺             | Stack pointer H SPH           |                            | R<br>≪      | Undefined         | 003C <sup>H</sup> | ROM bank register                 | DMBR  | R.W   | *0000000      |

| 001D∺             | Stack pointer L SPL           | ر<br>ا                     | R/W         | Undefined         | н О03 Он          | VRAM page register                | DMVP  | R/W   | 00****        |

| 001Ен             | Processor status register 0   | PS0                        | R/W         | Undefined         | 003Ен             | Reserved                          |       |       | •             |

| 001F∺             | Processor status register 1   | PS1                        | R⁄W         | 0***              | 003Fн             | Reserved                          |       |       |               |

| OTEO.             |                               |                            |             |                   |                   |                                   |       |       |               |

Fig. 9-2 SM8521 Memory Map (2)

OTES .

(The register indicated by R/W includes the bit of special-purpose register for read). R indicates that the register is only for read. • R/W indicates that there is at least one bit in the register is capable of read/write.

\* indicates that the corresponding bit is undefined.

\*1 The most significant bit is read only.

| Address        | Register name                           | R/W      | Initial         | Address           | Register name            |        | ₽   | Initial   |

|----------------|-----------------------------------------|----------|-----------------|-------------------|--------------------------|--------|-----|-----------|

| 0040⊬          | SG control register SGC                 | S RW     | 0000***0        | +0900             | SG0 waveform register 0  | SG0W0  | R/W | Undefined |

| 0041⊬          | Rserved                                 |          | 1               | 0061⊬             | SG0 waveform register 1  | SG0W1  | R/W | Undefined |

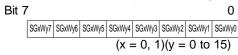

| 0042⊬          | SG0 output level control register SG0L  | - R/W    | 00000***        | 0062⊬             | SG0 waveform register 2  | SG0W2  | R/W | Undefined |

| 0043⊬          | Rserved                                 | •        | 1               | ⊬E900             | SG0 waveform register 3  | SG0W3  | R/W | Undefined |

| 0044∺          | SG1 output level control register SG1L  | - R/W    | 00000***        | 0064⊬             | SG0 waveform register 4  | SG0W4  | R/W | Undefined |

| 0045⊬          | Rserved                                 |          |                 | 0065⊬             | SG0 waveform register 5  | SG0W5  | R/W | Undefined |

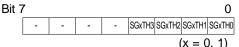

| 0046⊬          | SG0 time constant register (High) SG0TH | H R/W    | 0000****        | н9900             | SG0 waveform register 6  | SGOW6  | R/W | Undefined |

| 0047⊬          | SG0 time constant register (Low) SG0TL  | - R/W    | н00             | <sup>⊬</sup> 2900 | SG0 waveform register 7  | SG0W7  | R/W | Undefined |

| 0048⊬          | SG1 time constant register (High) SG1TH | H R/W    | 0000****        | H8900             | SG0 waveform register 8  | SG0W8  | W/W | Undefined |

| 0049⊬          | SG1 time constant register (Low) SG1Tl  | - R/W    | н00             | <sup>н</sup> 6900 | SG0 waveform register 9  | SG0W9  | R/W | Undefined |

| 004Ан          | SG2 output level control register SG2L  | - R/W    | 00000***        | 006Ан             | SG0 waveform register 10 | SG0W10 | R/W | Undefined |

| 004Вн          | Rserved                                 |          | 1               | н В900            | SG0 waveform register 11 | SG0W11 | R/W | Undefined |

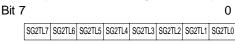

| 004C⊬          | SG2 time constant register (High) SG2TH | H R/W    | 0000****        | 006Сн             | SG0 waveform register 12 | SG0W12 | R/W | Undefined |

| 004Дн          | SG2 time constant register (Low) SG2T1  | - R/W    | н00             | нО900             | SG0 waveform register 13 | SG0W13 | R/W | Undefined |

| 004Ен          | SG-D/A direct output register SGDA      | <b>A</b> | +00             | н⊒900             | SG0 waveform register 14 | SG0W14 | R/W | Undefined |

| 004Fн          | Rserved                                 |          | 1               | н 1900            | SG0 waveform register 15 | SG0W15 | R/W | Undefined |

| 0020⊬          | Timer control register 0 TM0C           | S.<br>W. | 0000****        | 0070⊬             | SG1 waveform register 0  | SG1W0  | R/W | Undefined |

| 0051⊬          | Timer data register 0 TM0D              | C R/W    | +00             | 0071н             | SG1 waveform register 1  | SG1W1  | R/W | Undefined |

| 0052н          | Timer control register 1 TM1C           | RW       | 0000***0        | 0072⊬             | SG1 waveform register 2  | SG1W2  | R/W | Undefined |

| 0053⊬          | Timer data register 1 TM1D              | RW       | <sup>∺</sup> 00 | 9073⊬             | SG1 waveform register 3  | SG1W3  | R/W | Undefined |

| 0054⊬          | Clock timer CLKT                        | *        | н00             | 0074⊬             | SG1 waveform register 4  | SG1W4  | R/W | Undefined |

| 0055⊬          | Reserved                                |          | 1               | 9075⊬             | SG1 waveform register 5  | SG1W5  | R/W | Undefined |

| н9500          | Reserved                                | -        | -               | н9 <b>∠</b> 00    | SG1 waveform register 6  | SG1W6  | R/W | Undefined |

| н <b>∠</b> 200 | Reserved                                | -        | -               | н2200             | SG1 waveform register 7  | SG1W7  | R/W | Undefined |

| 0058⊬          | Reserved                                | •        | -               | н8700             | SG1 waveform register 8  | SG1W8  | R/W | Undefined |

| H6500          | Reserved                                |          | 1               | <sup>⊬</sup> 6200 | SG1 waveform register 9  | SG1W9  | R/W | Undefined |

| 005Ан          | Reserved                                |          |                 | 007Ан             | SG1 waveform register 10 | SG1W10 | R/W | Undefined |

| 005Вн          | Reserved                                |          | 1               | 007Вн             | SG1 waveform register 11 | SG1W11 | R/W | Undefined |

| 005Сн          | Reserved                                | •        | 1               | 007Сн             | SG1 waveform register 12 | SG1W12 | R/W | Undefined |

| 005Dн          | Reserved                                |          | -               | 007Дн             | SG1 waveform register 13 | SG1W13 | R/W | Undefined |

| 005Ен          | Watchdog timer register WDT             | R        | +00             | 007Ен             | SG1 waveform register 14 | SG1W14 | R/W | Undefined |

| 005Fн          | Watchdog timer control register WDTC    | S R/W    | 38н             | 907               | SG1 waveform register 15 | SG1W15 | R/W | Undefined |

| OTEO.          |                                         |          |                 |                   |                          |        |     |           |

Fig. 9-3 SM8521 Memory Map (3)

NOTES:

(The register indicated by R/W includes the bit of special-purpose register for read). R indicates that the register is only for read. • R/W indicates that there is at least one bit in the register which is capable of read/write.

\*1 Bits 0 to 5 are read only. Bits 6 and 7 are read/write.

<sup>\*</sup> indicates that the corresponding bit is undefined.

#### Hardware Reset

The hardware reset is an initial function for SM8521 system and comes from the following sources.

#### External reset

If the RESETB pin is applied to Low level in SM8521 operating, the hardware resets.

#### · Watchdog timer overflow

While watchdog timer overflows, the hardware resets.

The above 2 hardware reset sources initializate the system.

#### **OPERATING EXPLANATIONS**

#### Hardware reset operation

When the SM8521 is operating, a built-in pull-up resistor keeps the RESETB pin at High level. If external circuit (like as reset IC etc.) applies Low level voltage to RESETB pin, the SM8521 is reset by hardware after approximately two instruction cycles. To ensure hardware reset execution keeps

the RESETB pin at Low level over two instruction cycles of system clock.

The pin back to High level from Low level starts the warming up counter built-in SM8521. When the counter overflows, about 2<sup>18</sup> x main-clock leaves its hardware reset state and begins the program execution from the instruction at address 1020<sub>H</sub>. In the warming up interval, SM8521 is in HALT mode state.

Same as watchdog timer overflow case, the CPU leaves the hardware reset behind warming up period.

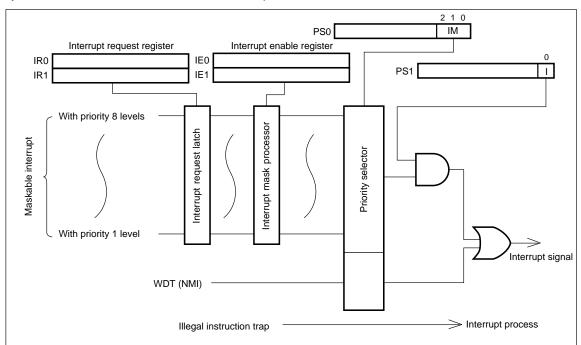

# Interrupt Function

The SM8521 supports 10 interrupt sources.

In these interrupts, watchdog timer and illegal instruction trap interrupts belong to non-maskable interrupts, the others, however, are maskable interrupts. 10 interrupt sources are shared to independent interrupt vector respectively, in the ROM address area between 1000H-101FH. And, the maskable interrupts are set 8 steps with priority level.

Fig. 10 Interrupt Block Diagram

| VECTOR LOCATION | INTERRUPT SOURCE               | SYMBOL  | PRIORITY* |

|-----------------|--------------------------------|---------|-----------|

| 1000н           | DMA                            | DMAINT  | 1         |

| 1002н           | Timer 0                        | TIMOINT | 2         |

| 1006н           | External interrupt             | EXTINT  | 3         |

| 1008н           | UART transmit/receive complete | UARTINT | 4         |

| 100Ен           | LCD controller                 | LCDCINT | 5         |

| 1012н           | Timer 1                        | TIM1INT | 6         |

| 1016н           | Clock                          | CKINT   | 7         |

| 101Ан           | Input/output port              | PIOINT  | 8         |

| 101Сн           | Watchdog timer overflow        | WDTINT  | _         |

|                 |                                |         |           |

Table 3 SM8521 Interrupt Vectors Location and Their Priority

#### **REGISTER EXPLANATIONS**

101Ен

# PS0 (Interrupt maskbit (IM) of processor status 0)

NMI, illegal instruction

The bits IM2-IM0 can set the acceptable level for interrupt. The maskable interrupt requested by CPU is set 1 to 8 priority levels. These bits IM2-IM0 determine processing interrupts which priority levels.

Bits 2 to 0 : Interrupt mask bits (IM2-IM0)

NMIINT, ILLINT

| BIT | CONTENT                               |

|-----|---------------------------------------|

| 000 | All maskable interrupts recognized.   |

| 001 | All maskable interrupts recognized.   |

| 010 | Maskable interrupts with 1 to 7 level |

| 010 | recognized.                           |

| 011 | Maskable interrupts with 1 to 6 level |

|     | recognized.                           |

| 100 | Maskable interrupts with 1 to 5 level |

| 100 | recognized.                           |

| 101 | Maskable interrupts with 1 to 4 level |

| 101 | recognized.                           |

| 110 | Maskable interrupts with 1 to 3 level |

| 110 | recognized.                           |

| 111 | Maskable interrupts with 1 to 2 level |

|     | recognized.                           |

#### NOTE:

When an interrupt enables by interrupt mask bit, if all interrupt conditions are setup, then the CPU starts to the interrupt processing.

<sup>\*</sup> The priority levels determine the order in which the chip process simultaneous interrupts. It also denotes the priority level of mask interrupts by setting the bits IM2-IM0 (bits 2-0 : PS0).

## PS1 (Interrupt enable bit (I) of processor status 1)

The bit I (bit 0 : PS1) enables/disables all maskable interrupts. After hardware reset, the bit I is set '0' and so all maskable interrupts are in disable state.

Bit 0 : Interrupt enable (I)

| BIT | CONTENT                                        |

|-----|------------------------------------------------|

| 0   | Disables to accept all maskable interrupts     |

|     | Enables to accept maskable interrupt. For      |

| 1   | each maskable interrupt can be enabled/        |

| '   | disabled by interrupt enable register IE0, IE1 |

|     | and bits IM2-IM0.                              |

Except that write to processor status PS1 directly, the bit I can be set/cleared by the following special-purpose instructions. (Under normal case, the special-purpose instructions are used.)

DI instruction: bit I is set '0'. El instruction: bit I is set '1'.

# IE0 (Interrupt enable register 0)

The interrupt enable register IE0 is an 8-bit readable/writable register containing the settings for enable/disable to accept interrupt sources.

| Bit 7 | 7   |      |   |        |      |   |   | 0    |  |

|-------|-----|------|---|--------|------|---|---|------|--|

|       | DMA | TIM0 | - | EXTINT | UART | - | - | LCDC |  |

Bit 7 : DMA interrupt enable bit

Bit 6: Timer 0 interrupt enable bit

Bit 5 : Sets '0'.

Bit 4 : External interrupt enable bit Bit 3 : UART interrupt enable bit

Bits 2 to 1 : Set '0'.

Bit 0 : LCD cotroller interrupt enable bit

| BIT | CONTENT |

|-----|---------|

| 0   | Disable |

| 1   | Enable  |

#### IE1 (Interrupt enable register 1)

The interrupt enable register IE1 is an 8-bit readable/writable register containing the settings for enable/disable to accept interrupt sources.

Bit 7 : Sets '0'.

Bit 6: Timer 1 interrupt enable bit

Bit 5 : Sets '0'.

Bit 4: Clock interrupt enable bit

Bit 3 : Sets '0'.

Bit 2 : PIO interrupt enable bit

Bits 1 to 0 : Set '0'.

| BIT | CONTENT |

|-----|---------|

| 0   | Disable |

| 1   | Enable  |

The interrupt enable register IEO and IE1 are also used to wake up the chip from standby mode (STOP mode, HALT mode) by setting the interrupt to enable. If the interrupt enabled by the interrupt enable register IEO and IE1 occurs, the chip will wake up from standby mode. But also there are interrupt sources which cannot use to wake up from STOP mode. For more details, refer to "Stand by Function".

## IR0 (Interrupt request register 0)

The interrupt request register IR0 is an 8-bit readable/writable register containing the setting for enable/disable to accept interrupt sources.

Bit 7 0

| DMA | TIMO | - | EXT | UART | - | - | LCDC

Bit 7: DMA interrupt request bit

Bit 6: Timer 0 interrupt request bit

Bit 5 : Sets '0'.

Bit 4 : External interrupt request bit

Bit 3: UART interrupt request bit

Bit 2 : Sets '0'. Bit 1 : Sets '0'.

Bit 0 : LCD controller Interrupt Request bit

| BIT | CONTENT |

|-----|---------|

| 0   | Disable |

| 1   | Enable  |

# IR1 (Interrupt request register 1)

The interrupt request register IR1 is an 8-bit readable/writable register containing the setting for enable/disable to accept interrupt sources.

Bit 7 0

Bit 7: Sets '0'.

Bit 6: Timer 1 interrupt request bit

Bit 5 : Sets '0'.

Bit 4: Clock interrupt request bit

Bit 3: Sets '0'.

Bit 2 : PIO interrupt request bit

Bit 1 to 0 : Set '0'.

| BIT | CONTENT |

|-----|---------|

| 0   | Disable |

| 1   | Enable  |

The interrupt request register IR0 and IR1 are also used to wake up the chip from standby mode (STOP mode, HALT mode) by setting the interrupt to enable. If the interrupt enabled by the interrupt request register IR0 and IR1 occurs, the chip will wake up from standby mode. But also there are interrupt sources which cannot use to wake up from STOP mode. For more details, refer to "Standby Function".

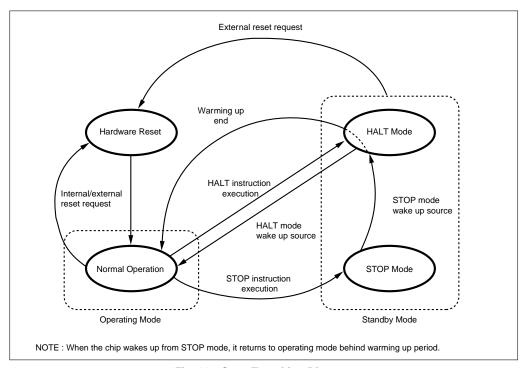

# **Standby Function**

The standby function is a function which temporarily stops program execution so as to conserve power. The standby mode is when the chip enters temporary stop state from the operating state, executing program. It contains both STOP and HALT modes, either of which can be selected according to your desires.

If the CPU executes the STOP mode or HALT mode, the chip will switch to standby mode from an operating mode. If the wake up source of the standby mode encounters an interrupt the chip returns to operating mode from the standby mode. Fig. 11 shows its state transition diagram.

Fig. 11 State Transition Diagram

#### NOTE:

The STOP instruction is also used for clock change function, which its operation is different from switching the chip to STOP mode, take care to use it.

|                   |                    | HALT MODE                  | STOP MODE                                               |

|-------------------|--------------------|----------------------------|---------------------------------------------------------|

| Transition method |                    | HALT instruction execution | STOP instruction execution                              |

| Wake up method    |                    | Hardware reset, interrupt  | Hardware reset, interrupt*1                             |

|                   | CPU                | Stop                       | Stop                                                    |

|                   | Main-clock         | Operating                  | Stop                                                    |

|                   | Sub-clock          | Operating                  | Operating                                               |

|                   | RAM, register      | Remain*2                   | Remain*2                                                |

|                   | I/O port           | Remain (interruptable)     | Remain (interruptable)                                  |

| Function          | Timer              | Operating                  | The timer used main-clock as counter clock is stop. It  |

| blocks            | Timei              | Operating                  | used external clock as counter clock can still operate. |

|                   | Capture trigger    | Operating                  | Stop                                                    |

|                   | UART               | Operating                  | Stop                                                    |

|                   | LCDC               | Operating                  | Stop                                                    |

|                   | Waveform generator | Operating                  | Stop                                                    |

Table 4 System State at Standby Mode

# \*2 General registers, control registers, and the other memory content all are remained. But something will be changed for the operatable blocks at STOP mode (for example, interrupt flag register IR0, IR1 content, etc.)

#### ABOUT HOU TO USE HALT MODE AND STOP MODE

The chip switches back to the operating mode from the HALT mode immediately after the wake up sources are encountered. For this reason, the HALT mode is more suitable for systems that need to be immediately woke up frequently. And, all interrupt sources (other than illegal instruction trap) can wake up the chip from the HALT mode.

Switching back to the operating mode from the STOP mode after the wake up sources are encountered must pass a warming up period. In addition, the function blocks used by the main-clock cannot be used in the wake up from STOP mode. Since the sampling circuit is stopped, it can not accept the PINTo input, either.

For this reason, the STOP mode (conserving more power than the HALT mode) is suitable for systems that can easily support the longer time that it will take to get, back to the operating mode (warming up period) .

Before switches to standby mode, in order to reduce to the current through every pins, set with program.

<sup>\*1</sup> The interrupts used to wake up the chip from STOP mode only have the external interrupts and the internal interrupts generated by operatable Timer, and SIO.

# **I/O PORTS**

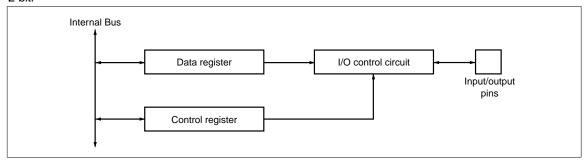

The SM8521 supports four 8-bit I/O ports. Each port can be selected one out of input, outpit, input with built-in pull-up resistor and open-drain in each 2-bit.

Fig. 12 PIO Block Diagram

## P0 to P3 (PIO data register)

| Bit 7 | 7   |     |     |     |     |      |       | 0     |

|-------|-----|-----|-----|-----|-----|------|-------|-------|

|       | Px7 | Px6 | Px5 | Px4 | Px3 | Px2  | Px1   | Px0   |

|       |     |     |     |     |     | (x = | 0, 1, | 2, 3) |

#### NOTE:

In case of reading P0-P3 register on condition that control register is input state, data of those pins is read. In case of on condition that control register is output state, data of register is read.

# P0C to P2C (PIO control register)

#### Bits 7 to 6:

| BIT | CONTENT                       |

|-----|-------------------------------|

| 00  | Input                         |

| 01  | Input (with pull-up resistor) |

| 10  | Output                        |

| 11  | Output (open-drain)           |

#### Bits 5 to 4:

| BIT | CONTENT                       |

|-----|-------------------------------|

| 00  | Input                         |

| 01  | Input (with pull-up resistor) |

| 10  | Output                        |

| 11  | Output (open-drain)           |

#### Bits 3 to 2:

| BIT | CONTENT                       |

|-----|-------------------------------|

| 00  | Input                         |

| 01  | Input (with pull-up resistor) |

| 10  | Output                        |

| 11  | Output (open-drain)           |

#### Bits 1 to 0:

| BIT | CONTENT                       |

|-----|-------------------------------|

| 00  | Input                         |

| 01  | Input (with pull-up resistor) |

| 10  | Output                        |

| 11  | Output (open-drain)           |

# P3C (Control register)

Bit 7 0 P3C7 P3C6 P3C5 P3C4 P3C3 P3C2 P3C1 P3C0

#### Bits 7 to 6:

| BIT | CONTENT                                    |

|-----|--------------------------------------------|

| 00  | Input                                      |

| 01  | Input (with pull-up resistor)              |

| 10  | Output/(Timer 1 clock outputs through P37) |

| 11  | Output/(Timer 1 clock outputs through P37) |

#### Bits 5 to 4:

| BIT | CONTENT                       |

|-----|-------------------------------|

| 00  | Input                         |

| 01  | Input (with pull-up resistor) |

| 10  | Output                        |

| 11  | Output (open-drain)           |

## Bits 3 to 2:

| BIT | CONTENT                       |

|-----|-------------------------------|

| 00  | Input                         |

| 01  | Input (with pull-up resistor) |

| 10  | Output                        |

| 11  | Output (open-drain)           |

# Bits 1 to 0:

| BIT | CONTENT                       |

|-----|-------------------------------|

| 00  | Input                         |

| 01  | Input (with pull-up resistor) |

| 10  | Output                        |

| 11  | Output (open-drain)           |

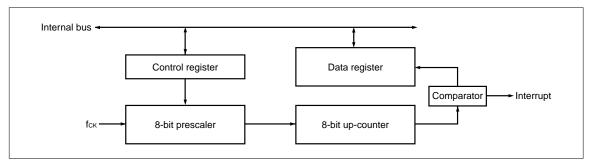

# **TIMER/COUNTERS**

The SM8521 supports 8-bit timer x 2, and clock timer x 1. One out of 8-bit prescaler output can be selected as an 8-bit timer input.

Fig. 13 8-Bit Timer Block Diagram

# 8-BIT TIMER REGISTER

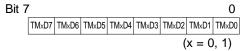

# TM0C, TM1C (Control registers)

| Bit 7 | 7     |       |       |       |       |       |       | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|       | TMxC7 | TMxC6 | TMxC5 | TMxC4 | TMxC3 | TMxC2 | TMxC1 | TMxC0 |

|       |       |       |       |       |       |       | x = 0 | ), 1) |

Bit 7: Start/stop Bits 6 to 3: Set '0' Bits 2 to 0:

| PRESCALER | INPUT CLOCK FOR 8-BIT UP-COUNTER |

|-----------|----------------------------------|

| 000       | fck/2                            |

| 001       | fcк/1 024                        |

| 010       | fcк/2 048                        |

| 011       | fcк/4 096                        |

| 100       | fcк/8 192                        |

| 101       | fcк/16 384                       |

| 110       | fcк/32 768                       |

| 111       | fcк/65 536                       |

#### TM0D, TM1D (Data register)

Bits 7 to 0 : Content of counter (read), time constant (write)

#### NOTES:

- After reset, the status of both TM0C and TM1C becomes 0\*\*\*\*000B, and both TM0D and TM1D becomes 00000000B.

- Every time between the value of 8-bit up counter and the value of time constant register coincide in timer execution, output signal inverts.

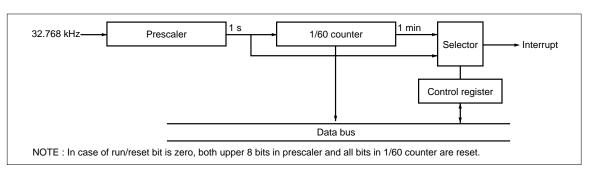

## **Clock Timer**

Clock timer is for real time clock. Dividing sub-clock (32.768 kHz), 1 s or 1 min interrupt occurs.

Fig. 14 Clock Timer Block Diagram

## **CLOCK TIMER REGISTER**

# **CLKT (Clock timer register)**

Bit 7: Run/reset

| BIT | STATUS        |

|-----|---------------|

| 0   | Counter reset |

| 1   | Run           |

Bit 6: Minute/second

| BIT | STATUS   |

|-----|----------|

| 0   | 1 second |

| 1   | 1 minute |

Bits 5 to 0 : Value of counter (read only)

# Watchdog Timer Register (WDT) PRS2 (Prescaler 2)

Prescaler PRS2 generates the count clock to watchdog timer counter WDT.

The following conditions are to clear all bits of prescaler PRS2.

- When hardware reset.

- When watchdog timer counter WDT stopped.

- When counter WDT is cleared by writing '1' to the bit WDTCR (bit 3 : WDTC).

Prescaler PRS2 divides the frequency derived from input clock  $fc_{10}$  (204.8 µs : main-clock = 10 MHz), then  $fc_{11}$ - $fc_{15}$  are output.

## WDT (Watchdog timer counter register)

Watchdog timer counter WDT is an 8-bit read only register which counts up from input clock.

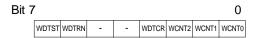

#### WDTC (Watchdog timer control register)

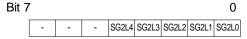

Watchdog timer control WDTC is an 8-bit read only register which sets watchdog timer to start/stop, counter clear designation, and selects the count clock.

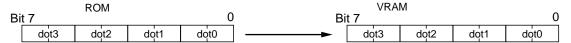

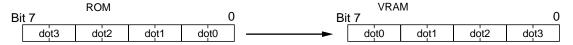

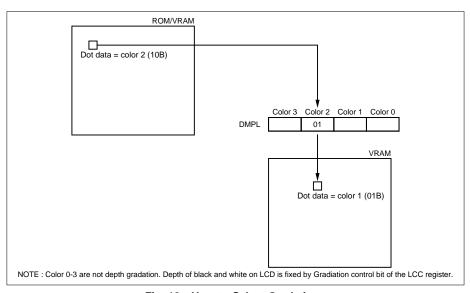

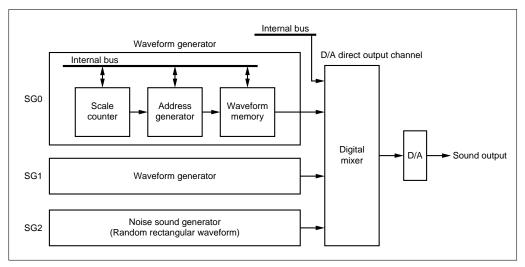

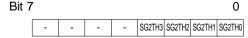

Bit 7: Watchdog timer start/stop bit (WDTST)